Frequency Divider (Pembagi Frekuensi)

Frequency divider atau pembagi fekuensi dapat dibuat dengan memanfaatkan kondisi togle pada suatu flip-flop digital. Togle flip-flop dapat dibuat dengan Data flip-flop (D-FF) maupun JK flip-flop (JK-FF). Satu unit togle flip-flop pada dasarnya akan meberikan output dengan frekuensi setengah frekuensi input atau dengan kata lain 1 unit togle flip-flop adalah pembagi 2 frekuensi input. Konsep dasar pembagi frekuensi menggunakan counter digital diawali dari kondisi togle pada suatu flip-flop tersebut. Diagram blok pembagi 2 frekuensi dari togle filp flop dapat diuraikan sebagai berikut. Pembagi 2 Frekuensi (Togle Flip-Flop)

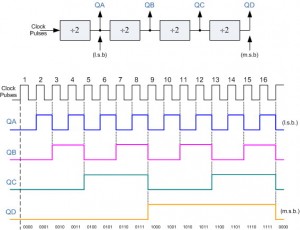

Dapat dilihat dari gambar diagram blok dan timing diagram dari sebuah pembagi 2 frekuensi yang memanfaatkan kondisi togle dari sebuah D-FF. Data Flip-Flop (D-FF) diatas diset sebagai Togle Flip-Flop (T-FF) dengan cara mengembalikan output Q ke input D dari D-FF tersebut. Dengan konfigurasi tersebut D-FF menjadi T-FF sehingga membentuk pembagi 2 frekuensi input. Kondisi diatas akan membuat output Q akan berubah setiap 2 kali pulsa clock diberikan, kondisi seperti ini disebut juga sebagai “riple counter”. Pembagi Frekuensi (Frequency divider) Dengan Asynchronous BCD Counter Counter seperti telah dijelaskan pada bab sebelumnya, akan menghitung jumlah data yang diberikan. Konsep dasar asynchronous counter digital inilah yang digunakan sebagai pembagi frekuensi dengan istilah atau pemahamam yang digeser dilihat dari sudut pandang frekuensinya yaitu, frekuensi output sebuah counter akan bernilai setengah dari frekuensi inputnya. Dengan statemen tersebut suatu counter BCD 4 bit dapat digunakan sebagai pembagi frekuensi hingga 1/16 karena setiap tahap dari sebuah counter akan memberikan output yang frekuensinya 0.5 dari frekuensi input. Atau dengan n bit BCD counter akan memberikan nilai pembagian frekuensi output 2n, sehingga untuk counter 4 bit maka pembagian frekuensi maksimumnya adalah 24 = 16. Berikut adalah pembagi frekuensi yang di bangun dengan counter 4 bit.

Dari gambar rangkaian dan timing diagram diatas terlihat bahwa setiap JK-FF akan memberikan pulsa output dengan frekuensi 0.5 dari frekuensi inputnya sehingga pada output terakhir QD memiliki frekuensi 1/16 frekuensi clock rangkaian pembagi frekuensi.

Everything that might be interesting

-

Pengertian Thyristor dan Jenis-jenis Thyristor Pengertian Thyristor dan Jenis-jenisnya – Thyristor adalah komponen elektron...

-

pengertian flip-flop Flip-flop merupakan rangkaian dari gerbang logika yang berfungsi untuk menyimpan suatu keadaan secara semi permanen...

-

Simbol dan Fungsi Kapasitor beserta Jenis-jenisnya Simbol dan Fungsi Kapasitor beserta jenis-jenisnya – Kapasitor (Capacitor) ata...

-

Sensor Elektronika dan Transduser 1. Pengertian Sensor dan Transduser Sensor dan transduser merupakan peralatan atau komponen...

-

Pengertian Resistor dan Jenis-jenisnya Pengertian Resistor dan Jenis-jenisnya – Resistor merupakan salah satu komponen yang paling ...

Random Posts

Random Video Tutorial

Isi Blog

- October (6)

- April (1)

- February (7)

- January (11)

- December (5)

- September (1)

- August (1)

- July (4)

- April (2)

- August (1)

- August (1)

- July (1)

- May (37)

- January (1)

- November (1)

- October (1)

- September (6)

- July (1)

- June (4)

- May (6)

- November (2)

- May (12)

- March (7)

- January (7)

- September (3)

- July (1)

- April (1)

- March (1)

- December (1)

- August (1)

- July (4)

- April (8)

- March (4)

- February (8)

- January (5)

- December (21)

Copyright ©

TEKNIK AUDIO VIDEO | Powered by SMKN 53 JAKARTA

Design by a71_5@yahoo.com